電路設計專欄 — 傳輸線概念的阻抗匹配

阻抗匹配就像【中庸】的概念一樣,凡事過猶不及。包含對他人的善意指導,同菜根譚:「攻人之惡,毋太嚴,要思其堪受;教人之善,毋過高,當使其可從。」

在電路中常見的時脈線路阻抗匹配:

〔Clock Buffer RD〕+〔Source Terminator RS〕=〔PCB Trace Impedance RPCB〕→ Impedance Matching

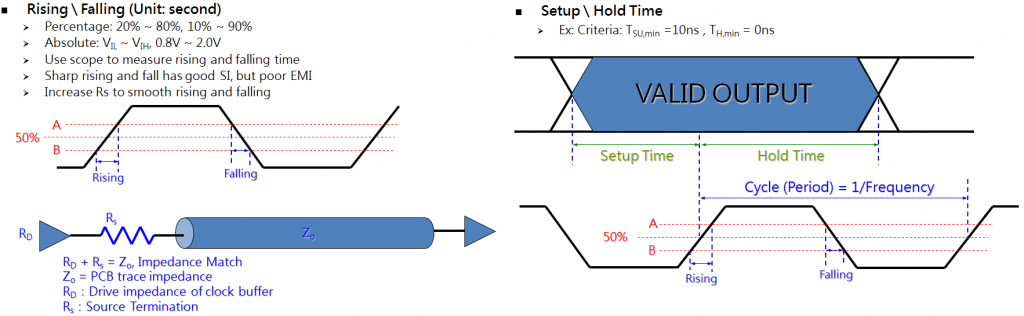

在阻抗匹配的設計下,較少的入射損失(IL) & 反射損失(RL)、較佳的波形、較足裕擷取資料時間(Setup / Hold Time)、較低能量的電磁干擾(EMI)。

時脈與擷取資料時間

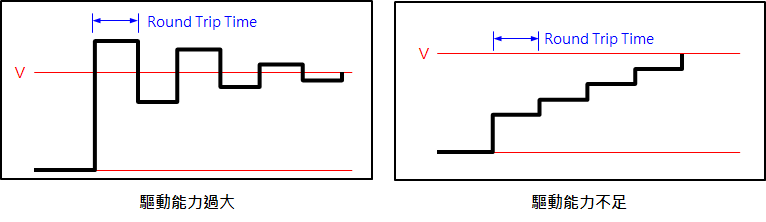

當驅動力過大時 ( RS過小),時脈波形會有Overshoot / Undershoot,則可能會造成擷取訊號誤動作 (Ex:Double Trigger),及較高的電磁干擾(EMI)。職場也是雷同,個人過度地積極進取或者超負載地驅動部門,反而干擾原定的人、事、物運作,造成部門步調不協調。而自己內心激盪的心情,久久不能平息。

當驅動力不足時 ( RS過大),時脈波形會有Rising / Falling過緩,同樣造成擷取訊號誤動作 (Ex:Setup / Hold Time不足)。職場也是相仿,成功包含「速度、力道、堅持」,無法Time To Market,再完美的設計都是枉費。

時脈驅動能力